# Teaching an Old Dog New Tricks: Verifiable FHE Using **Commodity Hardware**

Jules Drean MIT CSAIL

Fisher Jepsen MIT CSAIL

G. Edward Suh NVIDIA / Cornell University

Srinivas Devadas MIT CSAIL

Aamer Jaleel **NVIDIA**

Gururaj Saileshwar University of Toronto

### **Abstract**

We present Argos, a simple approach for adding verifiability to fully homomorphic encryption (FHE) schemes using trusted hardware. Traditional approaches to verifiable FHE require expensive cryptographic proofs, which incur an overhead of up to seven orders of magnitude on top of FHE, making them impractical.

With Argos, we show that trusted hardware can be securely used to provide verifiability for FHE computations, with minimal overhead relative to the baseline FHE computation. An important contribution of Argos is showing that the major security pitfall associated with trusted hardware, microarchitectural side channels, can be completely mitigated by excluding any secrets from the CPU and the memory hierarchy. This is made possible by focusing on building a platform that only enforces program and data integrity and not confidentiality (which is sufficient for verifiable FHE, since all data remain encrypted at all times). All secrets related to the attestation mechanism are kept in a separate coprocessor (e.g., a TPM)-inaccessible to any software-based attacker. Relying on a discrete TPM typically incurs significant performance overhead, which is why (insecure) software-based TPMs are used in practice. As a second contribution, we show that for FHE applications, the attestation protocol can be adapted to only incur a fixed cost.

Argos requires no dedicated hardware extensions and is supported on commodity processors from 2008 onward. Our prototype implementation introduces 3% overhead for FHE evaluation, and 8% for more complex protocols. In particular, we show that Argos can be used for real-world applications of FHE, such as private information retrieval (PIR) and private set intersection (PSI), where providing verifiability is imperative. By demonstrating how to combine cryptography with trusted hardware, Argos paves the way for widespread deployment of FHE-based protocols beyond the semi-honest setting, without the overhead of cryptographic proofs.

## **Keywords**

Fully homomorphic encryption, trusted execution environment, transient execution attacks, microarchitectural side channels

#### Introduction

Fully homomorphic encryption (FHE) [35, 40, 53, 63] makes it possible to evaluate any logical circuit directly on encrypted data. In

This work is licensed under the Creative Commons Attribution 4.0 International License. To view a copy of this license visit https://creativecommons.org/licenses/bv/4.0/ or send a letter to Creative Commons, PO Box 1866, Mountain View, CA 94042, USA.

Proceedings on Privacy Enhancing Technologies 2025(3), 282-303 © 2025 Copyright held by the owner/author(s). https://doi.org/10.56553/popets-2025-0099

282

the client-server setting, it can be used to build other powerful cryptographic primitives such as private set intersection (PSI) [4, 42, 72, 95, 96], private information retrieval (PIR) [34, 36, 42, 77] or multi-party computation (MPC) [9, 48]. FHE also has many practical use cases including private contact discovery [99], private smart contracts [122], or private inference [102]. Reducing performance overhead (currently 3 to 7 orders of magnitudes over non-private computation) has been the main focus of the last decade of research, but other limitations of FHE are now becoming more relevant.

At the forefront of these issues, the fact that FHE-schemes are not secure when considering a malicious evaluator, or that existing FHE schemes lack notions of integrity, are significant limitations for realworld deployment [10, 31, 131]. First, if a malicious server is able to supply malformed ciphertext for a client to decrypt, it can mount key recovery attacks [38, 69] and break all security (if the attacker recovers the private key, it can now decrypt the client's private requests). Second, if FHE enables delegation of computation on confidential data to an untrusted party, existing constructions cannot help the user verify that the correct function was evaluated. In other words, FHE schemes always assume honest-but-curious attackers. In the case of smart contracts, for instance, a malicious evaluator can completely change the functionality of the contract, with the option to even reveal confidential inputs and violate privacy. A straightforward solution is to add a layer of verifiable computation on top of the FHE scheme. Unfortunately, existing solutions suffer from major limitations. Cryptographic proofs incur an overhead of 4 to 6 orders of magnitude on top of FHE [131]. Another solution is to replicate the evaluation across several non-colluding parties, but distributed-trust setups are often impractical in the real world [87].

Trusted execution environments (TEEs) or secure enclaves [39, 46, 110, 121] have also been considered as a potential solution [81, 102, 131]. These technologies implement remote attestation, providing processors the capability to attest the code they are running, even in the presence of a privileged software attacker. TEEs offer better performance than cryptographic proofs, but come with weaker security guarantees: an attacker does not need to break a cryptographic assumption to forge a proof. Instead, the attacker needs to hack the platform or steal the attestation key. Still, these platforms initially seemed to offer a reasonable compromise. Unfortunately, a long series of published attacks (the SoK of Li et al. [85] covers 43 of them) quickly revealed that they were extensively vulnerable to microarchitectural side channels and transient execution attacks [33, 65, 118, 127, 129, 137]. These powerful attacks can be mounted in software and exploit microarchitectural structures and speculative mechanisms present in modern processors to extract secrets from trusted environments, not only violating confidentiality

of the protected programs but also extracting keys used for attestation. New microarchitectural side channels are discovered every year [97, 133] and the current consensus is that it will take many years of research to build software and hardware defense mechanisms that can efficiently eliminate these threats from modern processors. On top of this existential threat, the availability of TEEs is also limited. Modern platforms require dedicated hardware and are only available on server-grade processors, limiting adoption.

This Work. We present Argos, the first enclave platform specifically designed to build maliciously-secure and verifiable FHE. As observed in previous work [81, 102, 125, 131], for use cases where all application data is encrypted, such as in FHE, the only secrets exposed on the server are those used for attestation. We go further and show how this is a unique opportunity to rethink TEE architecture and design integrity-only enclaves that focus on data and code integrity without offering any confidentiality guarantee. Lessening the requirements for enclaves gives us the opportunity to 1) completely eliminate microarchitectural side channels by secluding all secret key material in a physically-separated coprocessor (such as a trusted platform module or TPM), 2) use a hypervisor-based TEE architecture that offers better performance and hardware compatibility, and 3) build a simplified attestation scheme that makes it possible to easily prove the security of our construction and amortize the cost of relying on a slow coprocessor for key operations.

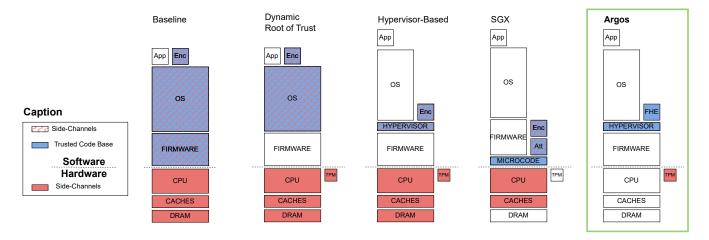

Eliminating Microarchitectural Side Channels. An important observation we make is that side-channel attacks are "readonly" gadgets and can be eliminated simply by excluding any secrets from the CPU and the memory hierarchy (see Figure 1). Softwaremounted side channels require an attacker program to share hardware resources with the victim programs in order to extract secrets. If all secrets are secluded on a separate chip, such as a physical trusted platform module (TPM) or a secure coprocessor [6, 44, 75], no attacker program can ever share microarchitectural resources with the cryptographic algorithm and extract secrets. Leveraging this insight, we design Argos to store all attestation secrets inside a discrete TPM and delegate all sensitive operations to outside of the CPU. This simple principle makes Argos secure by construction against side-channels. The only (side) channel left between the secluded cryptographic keys and a potential attacker is completion time [98] which is addressed through using constant-time cryptography in the TPM (see our threat model in Section 2).

Rehabilitating Hypervisor-based TEEs. Argos relies on a hypervisor-based TEE design. A security monitor runs with hypervisor privilege and provides code integrity and isolation to enclave programs. Such TEEs were introduced by TrustVisor [93] and are still widely used by cloud vendors to implement confidential computing [7]. These architectures are usually considered less secure than dedicated hardware platforms such as Intel SGX or AMD-SEV as they do not encrypt main memory and offer no security against Coldboot [70], one of the most practical physical attacks (see Table 7). In our context, this is not an issue as no secrets are ever exposed to main memory. As a result, despite our strong threat model, Argos can adapt this architecture to bring compatibility with most commodity hardware. In terms of performance, existing platforms typically rely on virtual TPMs [115]—one per execution environment—that are endorsed by the root TPM but executed on

CPU [12, 14]. While this approach avoids the performance bottleneck of a single physical TPM [93], it makes them vulnerable to microarchitectural side-channels. In contrast, Argos prefers a secure-by-design approach, centered on the discrete TPM.

**Performance Optimization With a Discrete Chip.** Relying on a single discrete TPM can have a significant impact on performance [94]. Nevertheless, we can still virtualize most TPM resources in the security monitor, trusted code that runs at hypervisor privilege level, as measurement (e.g., hashing) does not require any secret manipulation. Our use case also excludes the use of the TPM "sealed" secret storage. That means we only use the TPM as a "signing oracle". This can still be expensive, especially when considering interactive cryptographic protocols that require repeated and attested message exchanges.

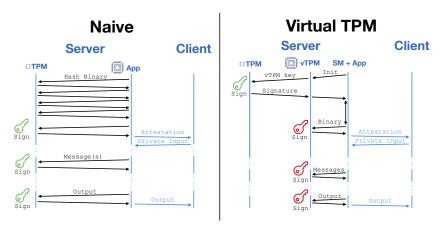

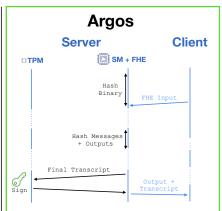

Simple and Efficient Attestation Scheme. We show that for our FHE applications, we can build a simple attestation scheme that only ever requires one TPM signature. Unlike in other enclave platforms, the remote user does not need to see any attestation proof before sending its sensitive data, as it will always stay encrypted. This also applies to intermediate protocol messages that do not need to be attested but simply added to a transcript whose hash is extended in the security monitor. At the end of the FHE computation (or more precisely, before any FHE ciphertext needs to be decrypted), the transcript's hash will be signed using the TPM. We show how our simplified transcript-based attestation can be model as a proof system, and show that it is sufficient to achieve malicious security needed for verifiable FHE. We also show how Argos can be extended to support batched verifiable FHE. As a result, the overhead of using a physical TPM becomes a fixed cost, and performance becomes similar to that of a virtual TPM, while enforcing security-with-abort in the presence of a malicious attacker [64].

**Extending Argos to FHE-Based Applications.** Circuit-level security sometimes differs from application-level security. In many FHE-based applications, a malicious server can provide corrupted inputs and gain some information from how the client behaves following decryption. This can have devastating downstream security implications. We show how Argos can easily be extended to support complex protocols in the malicious setting, such as authenticated PIR or authenticated PSI with almost no overhead compared to the semi-honest schemes.

Implementation and Evaluation. We implement and evaluate Argos on real hardware<sup>1</sup>. Our prototype runs on Intel x86 platforms, but Argos is easily adaptable to other vendors and architectures (e.g., AMD X86, ARM or RISC-V) and compatible with most commodity machines past 2008. To guarantee the TCB integrity at boot-time, we use commodity hardware root-of-trust technologies. Our prototype uses a TPM, but our architecture is adaptable to other hardware roots of trust and secure coprocessors such as the Apple Secure Enclave [6] or Open Titan [75]. Our security monitor is an open source fork of Tyche [30], modified to support our attestation scheme and remove side-channel protections, but our approach is also compatible with other micro-hypervisors like seL4 [78]. We implement a custom minimal runtime for FHE and the SEAL library [35], emulating system calls and providing randomness through a hardware random number generator (i.e., RDRAND instructions) that is not

<sup>&</sup>lt;sup>1</sup>https://github.com/mit-enclaves/argos

under OS control. For more complex applications that require a broader class of system calls, Gramine [126] can be used for better compatibility, at the price of a larger TCB and some performance overhead (5× slower startup time, for example). Argos has a limited attack surface with a minimal trusted code base (TCB) of less than 18KLOC, plus the target FHE application ( $\approx$  50KLOC). Our evaluation shows that Argos is 80 times faster than previous work leveraging Intel SGX for FHE integrity [131] with a minimal average performance overhead of 3% for FHE evaluation. We show that Argos can be used to implement more complex protocols such as attested PIR and attested PSI with performance overheads under 8% and without the significant offline communication costs incurred by cryptographic solutions.

**Contribution.** Argos is the first TEE-based platform to enable maliciously-secure verifiable FHE while being secure against all known microarchitectural side channels, all at minimal overheads. Prior to this work, it was not obvious that TEEs in commodity hardware could achieve such strong security guarantees. Existing TEEs suffer from insecurity due to the fact that their remote attestation mechanisms are vulnerable to microarchitectural side channels (see Section 9.7). As a result, TEEs have thus far remained undesirable for cryptographic applications such as verifiable FHE. Argos is carefully designed such that only the TPM contains unencrypted secrets. The TPM uses a simple microarchitecture and is microarchitecturally isolated from the CPU, blocking all known microarchitectural side channels. This means that we can leverage the TPM as a "signing oracle" to design a simple, efficient, and secure remote attestation scheme. Furthermore, this simple solution addresses an important problem: the efficient deployment of FHE in real-world scenarios with malicious security.

To summarize, our main contributions are:

- Argos, the first integrity-only enclave platform designed to build maliciously-secure verifiable FHE;

- Argos can be used to build fully malicious and authenticated PSI and PIR schemes;

- Argos is secure by construction against microarchitectural side channels and transient execution attacks;

- Argos requires no specialized hardware and is compatible with commodity processors from 2008 onward; and

- Argos only incurs 3% average performance overhead for FHE computation, less than 8% performance overhead for complex protocols, and virtually no communication overhead;

#### 2 Threat model

Our goal is to ensure integrity of the data and computation running inside our enclave environment. Most importantly, we do not protect confidentiality of our programs, nor do we protect them against denial of service. We assume a strong adversary collocated on the server that has compromised the majority of the software stack including the OS, and can mount any microarchitectural side-channel and transient execution attacks. Because Argos is secure against all software-mounted side channels that underlie known transient execution attacks, we will refer to all these attacks as "microarchitectural side channels" throughout the rest of the paper. Our trusted computing base (TCB) consists only of a security monitor (18 KLOC) and our application, both assumed to be bug-free. We assume that

the hardware is *functionally* correct and that the TPM's cryptography is properly implemented with constant-time programming. Rowhammer and fault injection attacks are not as practical and are considered out of scope. We also protect against the majority of physical attacks (cold boot, BIOS tampering, physical side channels) on the main processor and DRAM, but for the rest of this paper, we will focus on software-mounted attacks and consider physical attacks out of scope. A primer on microarchitectural and physical attacks can be found in Appendix B. A detailed discussion on the remaining attack surface can be found in Section 9.7.

# 3 Background & Motivation

# 3.1 FHE Schemes And Client-Server Setup

We consider a client-server setup where a server evaluates a logical circuit on some client ciphertext obtained using an FHE scheme. An FHE scheme is usually defined as a tuple of algorithms (&.Gen, &.Enc, &.Eval, &.Dec). The client generates a key pair using &.Gen and encrypts some input x using &.Enc. The server then uses &.Eval to evaluate a circuit f on the ciphertext  $c_x$  and sends the resulting ciphertext  $c_y$  back to the client to decrypt using &.Dec. Concretely:

- $\mathcal{E}$ .Gen $(1^{\lambda}) \to (pk, sk)$

- $\mathcal{E}.\operatorname{Enc}_{key}(x) \to c_x$

- $\mathcal{E}.\text{Eval}_{pk}(c_x, f) \to c_y \text{ where } y = f(x)$

- $\mathcal{E}.\mathrm{Dec}_{sk}(c_y) \to y$

FHE schemes must enforce the following properties (see Appendix C.1 for formal definitions):

**Correctness.** A scheme is *correct* if any honest computation will decrypt to the expected result (i.e.,  $Dec_{sk}(c_y) = f(x)$  with high probability).

**Security.** All FHE schemes are secure against chosen plaintext attacks, which means that an attacker with the public key cannot distinguish between the encryption of two different messages of its choice.

## 3.2 Semi-Honest vs. Malicious Security

In a honest-but-curious or semi-honest setting, an attacker is allowed to observe intermediate messages and passively infer information in order to break security, but cannot deviate from the agreed-upon protocol. In a malicious setting, the attacker is much more powerful and allowed to deviate arbitrarily from the protocol, e.g., to lie to the victim or tamper with messages. The semi-honest setting is often used in theory, but has limited viability in a deployment context where assuming a malicious attacker is more realistic.

## 3.3 Why Does FHE Need Verifiability?

Most state-of-the-art FHE schemes are *insecure* to use in real-world settings [35, 40, 53, 63] where malicious security is generally required. Because these schemes are not CCA-secure [18], if an attacker is able to supply malformed ciphertexts and observe decryption outcomes (for example, by observing client behavior), it can mount key recovery attacks and completely compromise privacy [32, 38, 57, 69]. Beyond the "circuit-level" security, the absence of integrity for FHE schemes also has implications for FHE-based applications. A malicious server can arbitrarily modify the circuit

Figure 1: Evolution of the attack surface on TEE platforms. Enc: enclave program, Att: attestation enclave.

they evaluate on the encrypted data. Attacks on correctness are an obvious issue, but these can also translate to attacks on privacy at the application level. Let us take the example of private contact discovery. Alice wants to discover who among her contacts is using a private messaging service [99]. Alice encrypts her address book, which contains all of her contacts' private information, and sends it to the server. The server now has access to Alice's encrypted set of contacts. If malicious, it could simply return the entire set to Alice. This could mislead Alice into thinking that one of her friends (Bob) uses the messaging service. Consequently, Alice contacts Bob via the service, leaking his phone number. This would violate Bob's privacy and defeat the use of private contact discovery.

## 3.4 Why Do We Need a New TEE Platform?

Trusted execution environments (TEEs) provide hardware-based isolation for confidential programs while minimizing the trusted code base (see Figure 1). The existing TEE landscape spans from platforms that protect small "enclave" programs [11, 46, 110] to those that implement confidential computing for entire virtual machines [7, 39, 86, 121]. However, the discovery of numerous microarchitectural side channel and transient execution attacks has severely compromised their confidentiality guarantees. Side channel attacks exploit shared microarchitectural structures such as memory caches [25, 65], translation look-aside buffers (TLB) [66], branch predictors [1, 56], and DRAM controllers [132] to enable information leakage between security domains.

TEEs also provide integrity guarantees through remote attestation, allowing a remote client to verify the authenticity of the hardware and the initial state of the execution environment. However, even these attestation mechanisms have proven vulnerable to side-channel attacks that can extract secret keys used by platforms to sign attestation reports [33, 118, 129], leading the cryptographic community to lose faith in TEEs. On the other hand, discrete trusted platform modules (TPMs) and associated dynamic root of trust (DRoT) have long served as dedicated hardware for platform integrity and secure storage against software-based attackers. However, their discrete nature also creates a severe performance

bottleneck when attesting multiple security domains (Flicker [94] incurs 2-3 orders of magnitude overhead). Although TPM virtualization [12, 14, 93, 115] can address these performance issues, in turn, they expose sensitive key material to microarchitectural side channels (see Section 10 for a more detailed comparison of Argos and other platforms).

To rebuild trust in hardware security primitives, we must develop new systems that are both inherently secure against microarchitectural side channels and capable of outperforming functionally equivalent cryptographic solutions. We address this challenge by focusing specifically on FHE applications and building a TEE platform that *only enforces integrity* of the enclave program, which is sufficient for verifiable FHE since data remains end-to-end encrypted throughout the computation.

# 4 Insights & Design Principles

## 4.1 FHE Applications Do Not Expose Secrets

In FHE applications, no sensitive data is ever manipulated in clear. This has several implications that can help simplify the design of a TEE platform and the attestation protocol.

**No Secrets Exposed.** In a standard TEE platform, a central feature is to enforce the confidentiality of the execution environment. In FHE, all data is encrypted. As a result, the contents of our enclave program (i.e., the state of  $\mathcal{E}$ .Eval) is public. This means our application is not vulnerable to side channels, and we do not need to harden the execution environment against the usual threats.

**No Long-Term Secret Storage.** In typical TEE platforms, an important feature is the ability for an enclave program to *seal* secrets and recover them later. This property is usually tied to the identity (or the measurement) of the enclave program, and a secret can only be unsealed by a program that matches the correct measurement. This is, for instance, what is used in Bitlocker to only ever release the disk encryption key to a correctly booted system. TPMs and TEE platforms such as SGX all offer a seal operation. FHE evaluation does not require long-term secret storage, which significantly reduces the features required by the TEE.

No Need To Pre-Establish Trust Before Sending Inputs. In usual remote attestation protocols, the remote client first needs to verify the TEE attestation to establish trust. Only once it trusts the TEE to have been correctly setup will it send its encrypted private input. This is because the inputs will then be decrypted inside of the TEE. In our case, inputs are never decrypted, which means that the remote client does not need to establish trust before sending the encrypted input. This makes it possible to amortize the cost of attestation by only signing the final transcript of program inputs and outputs (see Section 5).

# 4.2 Eliminating Microarchitectural Side Channels Using A Physical TPM

Because our FHE-applications do not expose secrets, the only secret ever present on the server is the private signing key used in the attestation scheme. This is a much smaller attack surface than in usual TEE systems. We can take advantage of that opportunity to completely eliminate microarchitectural side channels by placing the signing key in a microarchitecturally-isolated physical TPM. Because no secrets are left on the CPU or in main memory, this effectively makes our platform completely secure against microarchitectural side channels.

**Side Channels Are Read-Only.** One important element to keep in mind is that side channels are "read-only" gadgets and can only extract secrets from a victim program. Specifically, a side channel cannot modify the state of a victim's program memory or change its control flow.

Side Channels Require Shared Resources. To mount a microarchitectural side channel, an attacker needs to trigger a transmitter that will access the secret and modulate a channel to transmit information to a receiver under the attacker's control. That means the transmitter and receiver programs need to share some microarchitectural state in order for the transmission to be possible.

Physical TPMs Are Microarchitecturally Isolated. TPMs are commonly implemented on a discrete chip or as firmware on a secure co-processor (we cannot secure software TPM running on the CPU). They communicate with the main CPU using a hardware bus. They do not share cache, nor any processor resources, with the CPU. They use their own private resources, like private memory and registers, that are only accessible to the TPM. As a result, if the secret key is kept in a physical TPM, it is microarchitecturally-isolated from the attacker and there is no possibility for the secret to be extracted through a CPU microarchitectural side channel. In addition, the microarchitecture of TPMs and secure co-processors is intentionally kept simple, avoiding features like caches or out-of-order execution. This prevents the existence of indirect microarchitectural side channels such as NetSpectre [120]. Intrusive physical attacks might still be possible but are outside of our threat model (see Section 9.7).

#### 4.3 System Overview

Our system is composed of several hardware and software elements (see Figure 1). The security monitor is a small ( $\approx$ 18 KLOC) trusted piece of code running at the hypervisor privilege level. It is in charge of enforcing isolation between the different security domains and integrity of the enclave programs. Isolation is enforced by hardware

mechanisms (see Section 8.2) and integrity is enforced through our attestation scheme (Section 5). The security monitor does not manipulate any secret key material and delegates all cryptographic operations that require a key to the physical TPM. Integrity of the security monitor is enforced by the dynamic root-of-trust mechanism (Section 8.1). Running on top of the security monitor, a large untrusted operating system is in charge of all resource allocations. It contains all the complex logic, for instance, for memory allocation or scheduling. It also provides many services for (enclave) applications such as networking, or I/O.

Running an Enclave Program. To setup a trusted execution environment and securely run an enclave program, the untrusted OS interacts with the security monitor through vmcalls to the hypervisor. On behalf of the OS, the security monitor will reclaim some resources (memory and cores) and allocate them to the enclave. Thanks to the isolation mechanisms under the control of the security monitor, the OS is now unable to modify the state of the enclave memory. The security monitor will also enforce some invariants (setting the page table correctly and zeroing regions where no content is loaded), ensure the correct binary is loaded, and attest the enclave initial state (see Section 5.4). Once loaded, the enclave can be started. The remote client sends inputs over the network. They are received by the OS and placed in shared memory so that the enclave can access them. Inputs are systematically copied to enclave's private memory before being used. Any output is also copied to shared memory and sent back to the client by the OS.

# 5 The Argos Attestation Scheme

#### 5.1 Existing Attestation Protocols

Attestation schemes are generally interactive protocols that involve several rounds of communication between a client and a server. First, before any sensitive data is sent, trust needs to be established between the execution environment running on the server side and the remote client. The client will send a challenge and receive an attestation report, endorsed by the manufacturer and attesting that a genuine piece of hardware has been correctly set up to instantiate a trusted execution environment. Once trust has been established, the enclave program and the remote client can perform key exchange and establish a trusted communication channel. They can then start communicating and running the expected application. Any message coming out of the enclave needs to be encrypted and attested using the private key generated inside of the enclave to prevent a malicious attacker from observing or tampering with the content of the messages. Similarly, every message from the remote client needs to be decrypted and its integrity verified.

## 5.2 Overhead of Using a Discrete TPM

One of Argos's design principles dictates that no secret key material should ever be present on the main CPU. This means that each enclave would need to delegate all key operations to a single physical TPM. Even if only considering integrity protection (signature of messages and attestation protocol), this implies that the TPM becomes a serious bottleneck for the platform. Performing a signature using a discrete TPM takes approximately 196 ms, and the numbers are similar for integrated TPMs. This can potentially be a significant overhead for any application that requires several rounds

Figure 2: Evolution of remote attestation protocols. The naive approach with a secure co-processor is inefficient as it requires several back and forth communications with the discrete chip. The virtual TPM approach is insecure as it manipulates sensitive keys in the CPU, exposing them to microarchitectural side channels. The Argos protocol is both secure and efficient.

of communication. However, Argos's focus on FHE applications allows us to minimize much of this overhead.

# 5.3 Attested Transcript for FHE Applications

Trust does not need to be established before sending encrypted data. Because intermediate results are also encrypted, privacy cannot be compromised until a ciphertext is decrypted. That means integrity only needs to be checked *just before* decrypting an output (see Section 6 for our security analysis). In other words, each message of the FHE application does not need to be individually attested. Instead, the integrity-protected security monitor can keep a transcript of all relevant data (i.e., all application inputs, intermediate results, and final output), and, only perform a single TPM signature over that transcript. This simplifies the attestation scheme and drastically reduces the cost of using a physical TPM as remote attestation is now a simple fixed cost (see Figure 2).

#### 5.4 Argos Attestation Scheme

**Measured Boot.** Upon boot, the hardware dynamic root of trust (DRoT) is used to derive a measurement of the Argos security monitor (see Section 8.1). This measurement is securely stored in the TPM registers (PCRs).

Enclave Setup. When a new enclave is initialized, the security monitor will allocate some of its private memory to the enclave transcript. During enclave setup, the security monitor measures the enclave binary and stores it in the transcript. In our specific case, the binary contains the FHE circuit, small public inputs (e.g., FHE parameters), alongside the logic to evaluate the circuit (the SEAL library in our case). It also contains the rest of the application logic. All the values of the relevant architectural registers that represent the initial state of the execution environment are also added to this measurement. For instance, the enclave initial program counter, page tables, the stack pointer and the addresses of shared memory used to communicate with the OS. The measurement of the binary and initial state unambiguously represent a function that takes inputs from shared memory and outputs results to it.

**Enclave Lifetime.** During the lifetime of the enclave, the transcript is appended with hashes of the data received and sent by the enclave. This includes all inputs and outputs.

Attesting the Transcript. Once the final output has been generated and the transcript extended with it, the application performs a special vmcall to the security monitor to request the attested transcript. The security monitor then leverages the TPM to obtain a signature over the transcript. The application will then be able to transmit the attested transcript to the remote client, along with the final output.

Client Verification. Upon receiving the result(s) and the attested transcript, the client first verifies the attestation. The verification of the attestation goes as follows: First, the client verifies that the key used to sign the transcript belongs to a genuine TPM (see Section A for more details). It then checks that the measurement for the security monitor contained in the transcript signature matches a reference measurement that is known to be correct (see Section 9.7 on how such a reference measurement can be obtained). Finally, it checks that the binary reference in the transcript corresponds to the correct FHE application and that it was evaluated on the input it provided. If all checks are satisfied, the verification is successful. In case of a verification failure, the server is behaving maliciously and the client aborts.

**Output Decryption.** If and only if verification succeeds, the client decrypts the FHE output.

## 5.5 Remote Attestation as a Proof System

Our simplified attestation scheme is now functionally equivalent to a proof system. We can formalize it as a tuple ( $\Pi$ .Gen,  $\Pi$ .Prove,  $\Pi$ .Verify). The server runs  $\Pi$ .Gen to generate a key pair. It can then use the private key to run  $\Pi$ .Prove and generate an attested transcript ( $\pi_y$ ) over some client input x, an application g (formally a function, in practice a binary and an initial state for the execution environment), and the resulting output g. Given the public key, the client can then run  $\Pi$ .Verify to verify that the attested transcript  $\pi_y$  is correct, that is, g = g(x). In summary, we have:

- $\Pi$ .Gen $(1^{\lambda}) \rightarrow (pk, sk)$

- $\Pi$ .Prove<sub>sk</sub> $(x, g) \rightarrow (y, \pi_y)$  where y = g(x)

- $\Pi$ .Verify<sub>pk</sub> $(y,x,\pi_y) \to \text{true/false}$  where the client accept the output is true

Additionally, our scheme satisfies these two properties (see Appendix C.2 for formal definitions):

**Completeness.** The system is *complete* if  $\Pi$ . Verify will always accept a honestly computed result, i.e., a correctly formed transcript where y = q(x).

**Soundness.** The system is *sound* if an adversary cannot make  $\Pi$ . Verify accept an incorrect answer i.e., a transcript where  $y \neq q(x)$ .

**Modeling Several Rounds of Communication.** For applications that require several rounds of communication, we only generate one attested transcript at the end (see Section 5.3). That means x is the concatenation of all client inputs/messages. Our specific implementation simply shares intermediate results (the server messages) with the client. It also caches some internal state for  $\Pi$ .Prove (such as the measurement of g) so it can efficiently generate the final attested transcript once provided with all client inputs.

Security Analysis. Completeness of our attestation scheme reduces to the correctness of the underlying signature scheme used in the TPM. Soundness is more complex to establish, as it requires informally laying down all of our system security. First, as we explained earlier, an attacker (as described in our threat model) is not able to extract the private key from the TPM. Second, the security of our DRoT guarantees that the security monitor was correctly loaded and its integrity cannot be compromised. Third, our assumption of the TCB tells us that the security monitor is correctly implemented and bug-free. As a result, attested transcripts will only be generated for enclaves that are correctly set up, loaded, and executed. Our assumption on the underlying hardware isolation mechanisms (execution modes and nested page tables) guarantees that the integrity of the enclave code and data is maintained over the course of its lifetime. Finally, the functional correctness of the hardware guarantees that when an enclave is run that implements functionality f on input x, the resulting output y = f(x). With all of this in place, the soundness of our attestation scheme reduces to the soundness of the TPM signature scheme.

#### 6 Circuit-Level Verifiable FHE

We first show how, using Argos, we can take a semi-honest FHE scheme and build a circuit-level verifiable FHE scheme that achieves malicious security. In Section 7, we show how we can extend Argos to satisfy application-level security.

In our client-server setup, all state-of-the-art FHE schemes [35, 40, 53] are *insecure* when considering a malicious server. Let us take a simple example where a client wants to outsource some sensitive computation to a server using FHE. Here, the server might be able to infer information regarding the decryption of a ciphertext by observing the client reaction. For instance, in FHE, if the noise in the ciphertext overflows a given threshold, client-side decryption might fail, which could lead to the client emitting a new request

to the server. This is not a problem if assuming an honest-butcurious server. However, if the server is malicious, it can tweak the response to the client in arbitrary ways and observe its reaction. This is equivalent to providing our attacker with access to a (limited) decryption oracle that outputs "success" or "failure" for ciphertexts under the attacker's control. This is already enough to mount keyrecovery attacks [38, 69] and break security of the FHE scheme (if the attacker recovers the private key, it can now decrypt the client's private requests). In fact, this is much more problematic than a simple "correctness" issue where the client would just get a wrong output. In this simple outsourcing scenario, enforcing integrity at the FHE-circuit-level is enough, as it prevents the attacker from providing malformed ciphertexts to be decoded. When the client receives the response from the Argos server, it will first verify the attested transcript to ensure that the correct circuit was evaluated on the correct inputs. If verification fails, the client aborts, does not decrypt the ciphertext, and detects malicious behavior from the server. If and only if verification succeeds, the client may decrypt the ciphertext with the guarantee that it was correctly formed.

#### 6.1 Definition

Inspired by the formalism of Viand et. al. [131], we define circuit-level verifiable FHE (vFHE) as follow. A vFHE scheme is defined as a tuple of algorithms (Gen, Enc, Eval, Verify, Dec). The client is equipped with a key pair (pk<sub>c</sub>, sk<sub>c</sub>) and the server with (pk<sub>s</sub>, sk<sub>s</sub>). The client uses Enc to encrypt some input x and obtains a ciphertext  $c_x$ . Using Eval, the server evaluates a circuit f over  $c_x$  and generates an encrypted output  $c_y$ , along with an attested transcript  $\pi_y$ . When the client receives the output, it will first verify the transcript is correct ( $c_y = f(c_x)$ ) and if and only if it is, use Dec to decrypt  $c_y$  and recover y. In summary:

- $Gen(1^{\lambda}) \rightarrow ((pk_c, sk_c), (pk_s, sk_s))$

- $\operatorname{Enc}_{\operatorname{pk}_c}(x) \to c_x$

- Eval<sub>pk<sub>c</sub>,sk<sub>s</sub></sub>  $(c_x, f) \rightarrow (c_y, \pi_y)$  where y = f(x)

- Verify<sub>pk<sub>s</sub></sub>  $(c_y, c_x, \pi_y) \rightarrow \to \text{true/false}$  where the client accept if true, aborts otherwise.

- $\operatorname{Dec}_{\operatorname{sk}_c}(c_y) \to y$

Formal properties can be found in Appendix C.3. Correctness is defined identically to a semi-honest FHE scheme (see Section 3.1). Security differs as our attacker is now malicious and can send arbitrary  $c_y$  values. We also add two properties compared to the vanilla FHE-scheme.

**Completeness.** A vFHE scheme is *complete* if Verify will always accept an honestly computed result.

**Soundness.** Finally, a scheme is *sound* if an adversary cannot make Verify accept an incorrect answer.

# **6.2 Putting Everything Together**

Let's consider an FHE scheme ( $\mathcal{E}$ .Gen,  $\mathcal{E}$ .Enc,  $\mathcal{E}$ .Eval,  $\mathcal{E}$ .Dec) and our remote attestation scheme ( $\Pi$ .Gen,  $\Pi$ .Prove,  $\Pi$ .Verify). Argos' construction is as follows:

- $$\begin{split} \bullet \ \ & \text{Gen}(1^{\lambda}) \to ((pk_{\mathcal{E}}, sk_{\mathcal{E}}), (pk_{\Pi}, sk_{\Pi})) \\ & \text{with } (pk_{\mathcal{E}}, sk_{\mathcal{E}}) = \mathcal{E}.\text{Gen}(1^{\lambda}) \text{ and } (pk_{\Pi}, sk_{\Pi}) = \Pi.\text{Gen}(1^{\lambda}) \end{split}$$

- $\operatorname{Enc}(x) \to c_x$  with  $c_x = \mathcal{E}.\operatorname{Enc}(x)$

- Eval $(c_x, f) \to (c_y, \pi_y)$  with  $(c_y, \pi_y) = \Pi.Prove(c_x, \mathcal{E}.Eval(., f))$

- Verify $(c_y, c_x, \pi_y) \to b$  with  $b = \Pi$ . Verify $(c_y, c_x, \pi_y)$ .

•  $Dec(c_y) \rightarrow y$  with  $y = \mathcal{E}.Dec(c_y)$

The key here is to use the attestation mechanism to attest the correct execution of  $\mathcal{E}$ . Eval(.,f) represented by the binary and initial state of the execution environment.

**Security Proof** — **Sketch.** Correctness of our construction reduces to the correctness of the initial FHE scheme. Similarly, completeness and soundness directly derive from the completeness and soundness of the attestation scheme. Security is more subtle. Remember that our initial FHE scheme is not secure if provided with malformed ciphertexts. That means we can only rely on the security of the underlying FHE scheme if our attacker cannot gain control over the ciphertexts. This is enforced by the verification step. If the client runs Dec on an output received from the server, that means the output and the transcript had to successfully pass Verify. If this is true and the attacker was able to supply a ciphertext of its choice, i.e.,  $c_y \neq \mathcal{E}.\text{Eval}(c_x, f)$ , that means the attacker was able to break the soundness of the underlying attestation system, which is a contradiction. As a result, our construction is secure, and we have successfully built a circuit-level verifiable FHE scheme. The full proof can be found in Appendix D.

Batching FHE Evaluations. Running Π.Prove is expensive (it requires a TPM sign operation). Because evaluations of different FHE circuits are independent, we can batch them for performance optimization and only produce one attested transcript for all these evaluations. Enc, Verify, and Dec are the same, and security still holds as long as Dec is never run if verification was not successful.

# 7 Extending Argos to FHE-Based Applications

Circuit-level security sometimes differs from application-level security. For instance, attacks on correctness can escalate to attacks on privacy (Section 3.3). Additionally, the security of our FHE schemes breaks if a malicious server is able to supply malformed ciphertexts for decryption (Section 3.3). This is potentially dangerous when, in many FHE-applications, the server itself can provide public or private inputs and act as a party in the computation. We explore two such applications, 1) private information retrieval, and 2) private set intersection. For each application, we discuss the challenges in deploying FHE-based schemes in a real-world setting and show how Argos can be extended to enforce malicious security.

## 7.1 Malicious Private Information Retrieval

Private information retrieval (PIR) allows a client to retrieve an element from a public database hosted on a remote server, without the server learning which element was requested by the client. PIR has many applications such as public-key directory [41], certificate transparency logs [72, 119], private web search [71] or private analytics [67]. PIR can be instantiated in a multi-server or single-server setting using a range of cryptographic primitives, but in this paper we focus on the state-of-the-art for single-server PIR which are FHE-based schemes [4, 72, 95, 96].

Most schemes assume a honest-but-curious server; however, this is not a realistic setup for real-world deployment. Furthermore, circuit-level integrity alone is not enough to enforce malicious security. A malicious server can always modify the values in the

database, which could break not only the correctness (send the wrong answer for a given query), but most importantly security (i.e., privacy of client input) by mounting *selective failure attacks* [82]. We show how Argos can be extended to secure semi-honest FHE-based PIR scheme in a malicious setting.

Defending Against Selective Failure Attacks. In these attacks, a malicious server chooses an entry in the database and replaces the entry with a value that it knows will cause a decryption failure. This is possible because in FHE, using an input that is not in the correct plaintext space (for instance, an integer that is too large) can lead to a malformed ciphertext, which will not decrypt properly. Because our attacker might be able to observe the client reaction to decrypting the output (e.g., the client will send the request again), if decryption fails, the attacker can infer with high probability that the client queried the malformed entry.

Circuit integrity is not enough here. Argos also needs to preprocess the public database and check that the server's public inputs belong to the plaintext space. If a check fails, Argos should abort the server execution and not serve any client request. Formally, this is equivalent to allowing server inputs w for f, and in our construction, wrapping  $\mathcal{E}$ . Eval in a function that evaluates  $\mathcal{E}$ . Eval if and only if w is well formed and aborts otherwise.

Authenticated PIR. So far, our malicious PIR scheme is only able to guarantee that the server performed the protocol using a wellformed database, but not a specific one. Adding authenticity to a PIR scheme is a desirable property and might be essential for some real-world deployments. For instance, in the case of a transparency log or a public-key directory, it might be essential to guarantee the correct database was queried. We take inspiration from previous work and solve this problem by having the server initially commit to the database. This assumes a reference commitment is available for the client to fetch out-of-band.2 Argos can easily be extended to support this functionality by adding a fresh commitment to the database (i.e., a hash or the root of a Merkle tree) to the attestation transcript. When receiving the response to its query, a client should first verify the attestation transcript, including that the database commitment matches the reference one. If the verification fails, it should abort. If (and only if) it succeeds, it should then decrypt the response and proceed. In our formalism, this is equivalent to extending Verify to take a reference commitment H(w) as an input, and tweaking soundness to ensure an adversary cannot make Verify accept a transcript  $\pi_y$  that does not contain the correct commitment. A detailed security *argument* can be found in Appendix E.

# 7.2 Malicious Private Set Intersection

Private set intersection (PSI) allows two distrusting parties with some private sets to compute the intersection of these sets without learning more information than the intersection itself. PSI has many applications, such as private contact discovery [99] or compromised credential checking [106].

Most efficient PSI protocols do not achieve (full) malicious security [34, 36, 42, 77]. Some constructions do [50, 103, 109, 114, 116,

<sup>&</sup>lt;sup>2</sup>This assumption is made by Authenticated PIR [41] but recent works [49, 52] have also shown how using a limited number of "validation queries", the client can verify with high probability that the committed database is correct.

117, 123] but at the price of high offline communication cost (see Section 9.5). Using a state-of-the-art semi-honest PSI [42] scheme based on FHE, we show how Argos can be extended to make the scheme fully secure against a malicious server. Here, the main difference from the PIR setup is that the server inputs are not public, but private. State-of-the-art FHE schemes are not circuit private. That means that the client might be able to learn information regarding the server's private input by looking at the noise contained in the output. FHE-based PSI schemes mask the server's input using oblivious pseudo random functions (OPRFs) to provide privacy for the server even in the presence of malicious clients. Moreover, the security of the FHE scheme is argued to also provide privacy for the client, even in the presence of a "malicious" server. This is because the ideal PSI functionality considered in these works assumes a limited attacker with no observability of the client reactions [34]. However, this might not hold in a real-world deployment, as we explained before.

**Verifiable PSI.** Once deployed in a real-world setting, the attacker might be able to observe some of the client's reactions. Attacks on correctness might have serious security implications, sometimes translating to attacks on privacy (see example of private contact discovery in Section 3.3). Fortunately, circuit-level integrity—as provided by Argos—can guarantee *verifiable* PSI, which means that verification of the attestation transcript succeeds if and only if the server correctly executed the PSI circuit on a private set. Nevertheless, for full malicious security, we still need to ensure that the server evaluates PSI over the *correct* set.

**Authenticated PSI.** If the server's input set is not authenticated, a malicious server can arbitrarily modify the dataset without detection. This can have serious security implications in deployment. For instance, in the case of compromised credential checking, Alice reaches out to Mozilla's server to ensure that her passwords were not compromised and are safe to use. If Alice indeed uses some compromised credential and the server is malicious, it could evaluate the PSI circuit on her private set, but using a malicious input set, crafted server side, ensuring no intersection is found. This might lead Alice to use her compromised credentials.

Similarly to Authenticated PIR, Argos can be extended to include a commitment to the dataset (e.g., a Merkle tree or hash-based commitment scheme) in the attestation transcript. Here too, a public commitment needs to be made available out-of-band to the client, through a transparency log, for instance. Upon receiving a response to its request, the client first verifies the transcript and aborts if it does not match the correct commitment. Formally, the extensions we made for PIR are almost sufficient, we just need to tweak the wrapper function over  $\mathcal{E}$ . Eval to match our PSI functionality. Instead of only checking that w is well formed, the wrapping function should compute the corresponding OPRF values for w. The server's privacy is guaranteed by the OPRF, the soundness of the attestation scheme, and the fact that commitment schemes are hiding i.e., they do not leak information about the server's set. The security argument can be found in Appendix F.

# 8 Implementation Details

# 8.1 Security Monitor

Our security monitor is based on the X86 version of Tyche [30], a Rust micro-hypervisor that exposes hardware resources and isolation primitives to better protect trust domains. Note that other "small" hypervisors such as XEN [17] are at least one order of magnitude larger or closed source. We implement our attestation scheme on top of Tyche, including support for the hardware TPM and the interface to manage attested transcripts. We are also able to simplify some aspects of the platform, for instance, by removing side channel protections from Tyche (e.g., cache and CPU flush). One of the implementation challenges was to adapt Tyche and the Linux driver to support large (i.e., several GBs) enclaves with our custom runtime and manage memory allocation accordingly. To enforce the integrity of the security monitor, we use the TPM and a dynamic root of trust (e.g., Intel TXT or AMD DRMT [60, 104]) to implement standard measure boot (see primer in Section A). At the end of this process, two TPM registers (PCRs) are set with hash values that uniquely identify the security monitor binary. Later, when the security monitor needs to attest an application transcript, it will load the transcript hash in a third PCR and request a TPM Quote (a signature over select PCRs).

# 8.2 Memory Isolation Primitives

We use hardware extensions for virtualization to enforce isolation between security domains [128]. Extended or nested page tables [20], as implemented by Intel VT-x or AMD-V, make it possible for a guest domain to have an entire address space available and create a level of indirection for memory management that is exclusively under the control of the hypervisor. That means no execution domain can access other execution domains' address space nor modify its content. Other virtualization technologies such as AMD-Vi and Intel VT-d make it possible to protect domains from arbitrary DMA accesses. We use these technologies in Argos to enforce memory isolation for our enclave programs.

#### 8.3 Custom Runtime

The execution environments provided by Argos are similar to baremetal environments with no OS support. That means no syscalls, no program loader, no memory allocation, nor access to shared libraries. A runtime is required to support programs and modern libraries like SEAL that leverage many services from the OS. Gramine [126] is such a runtime and is already supported by Tyche. It was conceived to securely run off-the-shelf applications on Intel SGX. As a result, it implements all Linux syscalls and also has extensive support for shared library and memory management. However, because of its versatility, it is rather large (20KLOC) and adds some non-negligible overhead [112]. In order to reduce the TCB and improve performance, we implement our own custom runtime. It is minimal (870LOC) and consists of a simple memory allocator [108] and a handful of syscall handlers required by our application. For instance, we implement our own open and read syscalls to supply randomness from RDRAND when an application attempts to read /dev/urandom. We write our runtime to interface with MUSL [101] by interposing on system calls and providing our own handlers.

| Component                  | LOC       |

|----------------------------|-----------|

| BIOS                       | 1.5M      |

| Linux                      | 28M       |

| Security Monitor           | 18K       |

| Runtime (Custom / Gramine) | 870 / 20K |

| SEAL Library [35]          | 20K       |

| Application                | 1K-20K    |

Table 1: Software Components and TCB Breakdown. Red columns are excluded from the TCB.

| Platform | Time   |

|----------|--------|

| Software | 42     |

| vTPM     | 136    |

| dTPM     | 195752 |

Table 2: Signing operation ( $\mu$ s).

|         | Setup | Attest | Term |

|---------|-------|--------|------|

| SGX2    | 953   | 7      | 274  |

| Nitro   | 3759  | 1      | 363  |

| Argos+G | 466   | 196    | 5    |

| Argos   | 85    | 196    | 10   |

Table 3: Fixed-cost operations on a 1GB enclave (ms).

That means all applications and libraries (including SEAL [35]) need to be compiled statically and linked using our MUSL library, which requires some engineering effort to port applications but makes it possible to obtain high performance *and* a very light runtime.

## 9 Evaluation

#### 9.1 Testbench

We prototype Argos on a local Dell Optiplex machine from 2017 equipped with an Intel Core i7-7700 processor clocked at 3.6GHz, a discrete TPM 2.0, and 8GB of RAM. We run our security monitor (adapted from Tyche [30] see Section 8.1) directly on the hardware and evaluate our benchmarks using our custom SEAL runtime or Gramine [126]. We run Ubuntu 22.04 with the Linux kernel v6.2 and SEAL 4.1 with the BFV scheme [23]. All benchmarks are single-threaded, compiled using clang++ with the O3 optimization level.

We compare Argos with two other TEE platforms that have the following specs. SGXv2 running on an Azure server equipped with an Intel Xeon Platinum 8370C CPU with a frequency of 2.80GHz. AWS Nitro Enclaves [11] running on an AWS server equipped with an Intel Xeon Platinum 8259CL CPU with a frequency of 2.50GHz. The SGXv2 setup uses Gramine as a runtime while Nitro Enclave uses a docker container environment that runs its own Linux kernel. Note that under our threat model, both SGXv2 and AWS Nitro Enclaves are *insecure* and are only used as comparison points for performance. See Table 7 for a more complete comparison. All numbers are obtained by averaging values over 10 runs.

# 9.2 TCB Evaluation

Detailed count for lines of code (LOCs) can be found in Table 1. Our TCB is small with a minimum of 40KLOC for our PIR application and a total of 60KLOC for our PSI application. Note that we did not account for SMM code, the microcode used in the DRoT, or the TPM as it is not public information, and we consider these elements as part of the hardware. This should be compared to other TEEs and system projects that try to keep a small footprint. For instance,

Nitro Enclaves include an entire Linux kernel which blows up their TCB in the range of MLOC, several orders of magnitude bigger than our TCB. On the other hand, SGX would not include the SMM code or the security monitor (18KLOC), but relies on a significant amount of microcode. As a point of comparison, XEN [17] (a popular mini-hypervisor), and Coreboot [21] (a minimal BIOS) each total 200KLOC. On the other hand, micro-kernels such as SeL4 [78] are in a similar size range with tens of thousands of lines of code.

#### 9.3 Microbenchmarks

**TPM Sign Operation.** We evaluate the cost of signing a 32-byte message (i.e., a hash) using a physical TPM. We also compare the incurred overhead with two insecure baselines: 1) software signature in the application and 2) software signature performed by the security monitor (vTPM). Results can be found in Table 2. The vTPM signature requires a vmcall and a context switch to the security monitor, which incurs a small overhead (about  $100\mu s$ ) compared to the application-level signature. Operations with the physical TPMs are comparatively slow: we measure 196ms to perform a signature (which in our case boils down to loading the hash value in a PCR and requesting a TPM quote). This is 3 orders of magnitude slower than a vTPM. Some modern chipset-integrated hardware TPMs are faster than discrete TPMs and are still microarchitecturally isolated from the CPU. However, they are only 5× faster than the discrete TPM at best. These results hint at the importance of Argos' optimized attestation scheme, which only requires at most one signature per FHE evaluation and even less when using batching.

Enclave Fixed Costs. We evaluate the different fixed costs of different operations over the lifetime of an enclave. To obtain measurements, we instrument a dummy enclave for which we allocate 1GB of memory. Setup time is measured between the time a command line program requests the operating system to start an enclave and when execution reaches the main function of the enclave application. This means it includes the allocation of enclave resources, loading of the binary, page table setup, binary measurement, and runtime initialization. We can see that Nitro Enclaves have the highest setup time mostly due to the fact that they contain an entire Linux kernel that needs to be booted. SGXv2 also presents some large startup time. This is mostly due to all the special instructions required to start an enclave and the time it takes Gramine to initialize. As indicated in Gramine's documentation, initialization can initiate more than 200 OCALLs, which all incur expensive context switches with architectural flushes (CPU caches and state) that  $\cos t 8,000 - 12,000$  cycles each [112]. This overhead can also be observed when running Argos with Gramine. In comparison, our custom runtime is initialized with minimal overhead, which might be essential for latency-sensitive applications.

Attestation time is the time it takes for an enclave to request an attestation quote. For SGXv2, support for remote attestation service by Intel is deprecated [45] so we use the analogue Microsoft Azure Attestation [111] scheme. Once provisioned, signing of the attestation quote is performed locally by the quoting enclave, hence the high performance similar to using a vTPM. For Nitro Enclaves, the attestation is performed by the hypervisor using a vTPM [12]

which also explains the high performance. Due to Argos's reliance on a physical TPM, we have a comparably slow attestation time.

Termination time is measured between when the enclave main function exits and when the control returns to the command-line program that launched the enclave. It includes all the time required to deallocate, clear resources, and return them to the OS. For SGX, that also implies a lot of cleanup at the hardware level. For Nitro Enclaves, it requires to wait for Linux to shutdown, which also adds delay. In Argos, since all sensitive data is encrypted, memory does not need to be sanitized before being reallocated to the OS.

**Transcript Size.** Our transcript is quite small and composed of 2 PCR values used by the DRoT, the initial value of some key registers for the execution environment, the hash of our binary, the hash of messages exchanged by the application, the hash of some server input if needed. It also contains the signature and the TPM public key along with the TPM certificates endorsed by the manufacturer. Concretely, we measure a small transcript size of only 1,407 bits, negligible in front of the size of an FHE ciphertext (≈500KB).

#### 9.4 FHE Evaluation

We evaluate the overhead of circuit-level vFHE in Argos compared to semi-honest FHE. Results can be seen in Table 4. We use the same benchmarks as previous work on vFHE [131] and compile and evaluate the different circuits using the SEAL library [35]. The results from Viand. et al. highlight the impractical performance overheads when using cryptographic proofs such as Bulletproofs [29], Aurora [19], Groth16 [68] or Rinocchio [61], to build vFHE: between 6 and 7 orders of magnitude, with the exception of Rinocchio for the Tiny benchmark. Their semi-honest baseline is also relatively slow, hinting that they might have disabled hardware acceleration. Their implementation of FHE-in-TEE also shows poor performance probably due to the limitation of SGXv1 (limited 128MB EPC memory and unreliable timers). For a fair comparison, we run the benchmarks of SGXv2 and Nitro Enclaves. We compiled the benchmarks on one machine and used the same binary across or different setups. Here, the performance looks much better with single-digit overheads and even small speedups for Nitro Enclaves. Indeed, once setup, running a program in an enclave is equivalent to running it with bare-metal performance. We tried to keep the runtime as similar as possible between the different configurations, but small differences might explain these results. For Argos, we evaluate two different configurations. One using the Gramine runtime (Argos+G) and one using our custom runtime. Our custom runtime performs better than Gramine. This might be for a couple reasons including that the MUSL library tends to be faster than Glibc, our custom runtime simply ignores interrupts sent by the OS scheduler (the enclave is not de-scheduled), and our custom syscall handlers handle less corner cases and are more efficient (for instance, to allocate memory). In conclusion, Argos shows performance comparable to commercial TEEs while offering better security. Our custom runtime makes it possible to reduce the TCB and improve performance at the cost of some engineering effort to port applications.

| Platform          | Tiny         | Small         | Medium        |  |  |

|-------------------|--------------|---------------|---------------|--|--|

| Baseline [131]    | 2ms          | 11ms          | 14ms          |  |  |

| Bulletproofs [29] | 7569s        | 3957s         | 8697s         |  |  |

| Aurora [19]       | 1554s        | 3750s         | 5028s         |  |  |

| Groth16 [68]      | 196s         | 473s          | 634s          |  |  |

| Rinocchio [61]    | 320ms        | 305s          | 443s          |  |  |

| SGXv1 [131]       | 154ms        | 1100ms        | 1260ms        |  |  |

| Baseline Azure    | 283us        | 1727us        | 3170us        |  |  |

| SGXv2 Azure       | 290us (+3%)  | 1840us (+7%)  | 3638us (+15%) |  |  |

| Baseline AWS      | 324us        | 1889us        | 3456us        |  |  |

| Nitro Enclave     | 317us (-2%)  | 1827us (-3%)  | 3450us (-0%)  |  |  |

| Baseline Local    | 351us        | 2341us        | 4376us        |  |  |

| Argos+G           | 392us (+12%) | 2702us (+16%) | 5202us (+19%) |  |  |

| Argos             | 352us (+0%)  | 2480us (+6%)  | 4447us (+2%)  |  |  |

Table 4: Time for FHE evaluation for three circuits. Baseline is always semi-honest FHE *without* integrity. Greyed values are reported from [131]. We indicate the overhead compared to the baseline on the same machine.

|          | ]     | Per Enclave |      | Per Ç | Query | Per Batch |  |

|----------|-------|-------------|------|-------|-------|-----------|--|

|          | Setup | Pre-Proc.   | Hash | Proc. | Hash  | Attest.   |  |

| Baseline | 3     | 2835        | N/A  | 1593  | N/A   | N/A       |  |

| Argos+G  | 1559  | 3192        | 465  | 1812  | 1     | 196       |  |

| Argos    | 158   | 2821        | 465  | 1610  | 1     | 196       |  |

Table 5: Breakdown of end-to-end execution times for authenticated private information retrieval (ms).

|          |    |       | Enclave   | Qu   | Batch |      |         |

|----------|----|-------|-----------|------|-------|------|---------|

|          | #C | Setup | Pre-Proc. | Hash | Proc. | Hash | Attest. |

| Baseline | 1  | 4     | 40351     | N/A  | 3231  | N/A  | N/A     |

| Argos+G  | 1  | 1576  | 44530     | 132  | 3732  | 187  | 196     |

| Argos    | 1  | 179   | 37054     | 105  | 3354  | 148  | 196     |

| Baseline | 3K | 4     | 40348     | N/A  | 3276  | N/A  | N/A     |

| Argos+G  | 3K | 1530  | 44467     | 131  | 3740  | 187  | 196     |

| Argos    | 3K | 175   | 36933     | 104  | 3403  | 148  | 196     |

Table 6: Breakdown of end-to-end execution times for private set intersection (ms). #C: size of the client set.

## 9.5 Authenticated Private Information Retrieval

We evaluate the overhead of authenticated PIR using Argos compared to semi-honest unauthenticated PSI. We use the SealPIR library from Angel et. al. [4]. We use the BFV scheme with polynomials of degree 4096. The plaintext modulus is set to 20. We evaluate performance for a database of size  $2^{20} \approx 1$ M where each element measures 128 bytes. We allocate 4GB of static memory to our enclave. We instrument the code to hash the database, queries, and responses and to attest the final transcript once all queries have been processed. Results can be found in Table 5. We compare two configurations for Argos. One using the Gramine runtime (Argos+G) and one using our custom runtime. For Argos+G, the server setup -which is a fixed cost- shows an overhead of +83% mostly due to overhead setting up the enclave (+55%) and hashing the database (+16%). For query processing, we measure an overhead of 13% for fetching one element. Here, hashing the response before sending it to the client takes a negligible amount of time. Taking

into account the signing of the final transcript, the overhead goes up to 26% for retrieving one element. Batching queries here would amortize costs down to a minimum of 13% for numerous queries. For Argos using our custom runtime, overhead goes down to 21% for setup (mostly due to hashing of the batabase) and 1% for query processing. This is due to our more efficient handling of system calls. The only cost left is attestation that can be amortized by batching requests (see Section 6.2). Once again, our custom runtime offers better performance than Gramine. For all setups, Argos's transcript incurs negligible (>1%) communication overhead.

Recent work on single-server authenticated PIR using cryptographic constructions by Colombo. et al., while providing better security guarantees, show a performance overhead of 30-100× [41]. Other recent work, VeriSimplePIR [49], shows more reasonable online overheads (13%-20%) but incurs significant offline communication of the same order of magnitude as the database itself (2GiB communication for a 4GiB dataset). This also makes updating the database extremely difficult, while our scheme only requires updating a Merkle tree and communicating the commitment.

#### 9.6 Authenticated Private Set Intersection

We evaluate the overhead of authenticated PSI using Argos compared to semi-honest non-attested PSI. We use the APSI library compatible with SEAL that implements the state-of-the-art FHEbased scheme from Cong et. al. [42]. We use the BFV scheme with parameters 8192 for the polynomial degree modulus and the coefficient modulus. The plaintext modulus is set to 65537. We evaluated the performance of the unlabeled scheme with a server set size of  $2^{20} \approx 1M$ . We allocate 4GB of static memory to our enclave. We instrument the code to hash the database, queries, and responses and to attest the final transcript once all queries have been processed. Results can be found in Table 6. For Argos+Gramine, the server setup phase, we measure an overhead of 15% mainly due to preprocessing operations, but with our custom runtime, we see a speedup of 8% due to our fast handling of memory allocation, and other syscalls. Hashing the database is negligible here. For query time, we see +16% and +8% overhead for Gramine and our custom runtime, respectively. For all setups, Argos incurs negligible communication (>1%). In comparison, the state-of-the-art for malicious PSI using a cryptographic construction [114] shows a 19% performance overhead and a 67% communication overhead compared to their own semi-honest construction for a dataset of 2<sup>20</sup> elements. However, they cannot guarantee that the server uses the same dataset across clients and require to compute and transfer a large commitment

Attested Transcript. Our remote attestation scheme makes it possible to amortize the cost of attestation over messages and queries. In the PSI scheme we use, each query requires two rounds of communication (one round for OPRF, and one for the query itself), plus one initial attestation, which would bring the overhead for one query to +27%. Instead, we only need to pay the cost of one attestation operation per batch. The PSI scheme we use already supports batching, but only up to a certain client set size (this is a limitation of FHE-based PSI schemes). For our given server set size, we empirically measure a non-negligible failure rate for client set size above 3000 elements. A client who would want to compute

the intersection of a bigger set would have to do so using several queries. That means that the maximum overhead of 15% for a client set size of 1 can be amortized for larger client set sizes. For instance, for a client set size of 30,000, computing the complete intersection would take 10 queries and overhead would be reduced back to 8%. This phenomenon would be heightened for more efficient PSI schemes as the cost of TPM signing is constant.

# 9.7 Analysis of the Remaining Attack Surface

Argos primarily defends against microarchitectural side channels, which constitute the vast majority of TEE attacks so far (43 published according to [85]). While Argos is vulnerable to fault injection [76, 100, 113] and Rowhammer attacks (less studied on TEEs), these threats are not fatal - software can be hardened against fault injections [26], and no Rowhammer attacks have demonstrated the capabilities needed to compromise Argos (gaining hypervisor privilege on a hardware VM). Regarding physical attacks, Argos protects against ColdBoot [70] and physical side channels on the CPU [83], but remains vulnerable to physical fault injection attacks [27, 37]. The TPM only exposes a minimal attack surface for physical side channels, and modern TPMs are now directly integrated into the SoC, significantly raising the bar for these attacks [74]. Indeed, integrated TPMs do not implement modern features such as DVFS or RAPL, making all known software attacks such as Hertzbleed [133] or PLATYPUS [89] and others [140] impossible. Other physical attacks are out-of-scope, but would still be significantly less practical: 1) CPU-noise most likely masks signals from small integrated TPM, 2) TPM cryptography is assumed constant-time, thwarting simple power and EM attacks [62, 92], 3) for constant-time code, side channels are sometimes due to advanced circuit optimizations [88], unlikely in a small integrated co-processor. Finally, our TCB might still contain bugs, and attacks that exploit implementation mistakes have been demonstrated on the Intel DRoT and the associated secure coprocessor [28, 43, 55, 135, 136]. However, these implementation errors can be patched when discovered —unlike vulnerabilities to microarchitectural side channel attacks.

#### 10 Related Work

TPMs and Hypervisor-based TEEs. Trusted platform modules (TPMs) combined with dynamic root-of-trust technologies have long served as dedicated hardware to enforce platform integrity. Flicker [94] proposes to use these two technologies combined to isolate and attest small pieces of application logic, or PALs while reducing the software TCB to a handful of lines of code. No keys ever leave the TPM in Flicker, which gives it the same resistance to microarchitectural side channels as Argos (even if not discussed in the paper at the time). However, their complete reliance on hardware mechanisms creates significant overheads, i.e., 2-3 orders of magnitude. Virtualization technologies (making their appearance in processors around 2008) aim at isolating different trusted domains in the form of virtual machines (VMs). They create a new privileged execution mode dedicated to the hypervisor and provide hardware primitives such as extended (or nested) page tables to enforce memory isolation between different security domains. These technologies identified the opportunity to virtualize the TPM [107] and provide confidentiality and integrity for trusted domains with

|                |       |              | Secu         | rity            |                  |                 | Usability    |              |                  | Performance |         |       |

|----------------|-------|--------------|--------------|-----------------|------------------|-----------------|--------------|--------------|------------------|-------------|---------|-------|

| TEE Platform   | ТСВ   | μ-arch<br>SC | Cold<br>Boot | Phys.<br>SC CPU | Fault<br>Inject. | Phys.<br>SC TPM | Availability | Dedic.<br>HW | Implementation   | Setup       | Attest. | Comp. |

| ZK Proofs      | Null  | P            | P            | P               | P                | P               | SW           | SW           | Open Source      |             |         |       |

| Nitro Enclaves | Large | V            | V            | V               | V                | V               | AWS          | Yes          | Closed Source    |             | + +     | + +   |

| Arm TrustZone  | Small | V            | V            | V               | V                | V               | High         | Yes          | HW Closed Source | +           | +       | _     |

| Intel SGX V1   | Small | V            | P            | V               | V                | V               | Deprecated   | Yes          | HW Closed-Source |             | +       |       |

| Intel SGX V2   | Small | V            | P            | V               | V                | V               | Cloud        | Yes          | HW Closed-Source |             | +       | +     |

| AMD SEV        | Large | V            | P            | V               | V                | V               | Cloud        | Yes          | HW Closed-Source |             | +       | + +   |

| Intel TDX      | Large | V            | P            | V               | V                | V               | Coming       | Yes          | HW Closed-Source |             | +       | + +   |

| ARM CCA        | Large | V            | P            | V               | V                | V               | Coming       | Yes          | HW Closed-Source |             | +       | + +   |